# MECE336 Microprocessors I Interrupts

Dr. Kurtuluş Erinç Akdoğan

kurtuluserinc@cankaya.edu.tr

Course Webpage: http://MECE336.cankaya.edu.tr

# Working With Time: Interrupts

### Our daily lives are ruled by time

alarm clocks to wake us

- Embedded systems, needs to respond in a timely manner to external events.

- These requirements are met primarily by feature of a microcontroller: the interrupt

- Interrupts form part of the exciting techniques that underpin real-time programming

# The Main Idea – Interrupts

#### Up to Now

- Programs are written in a precise and predictable fashion

- Instructions are followed in a clear order and the update of the program counter is well-defined at each step of the program

Interrupt Idea

- Function of an interrupt is to alert the CPU that some significant event such as power failure, the system overheating, has happened

- □ Interrupt can occur at any time

- Effect of an interrupt is generally to stop the CPU from doing its current task and to force it to respond to the interrupt cause

- Interrupt disturbs predictable execution of a program

- □ There can be different interrupt sources on a microcontroller

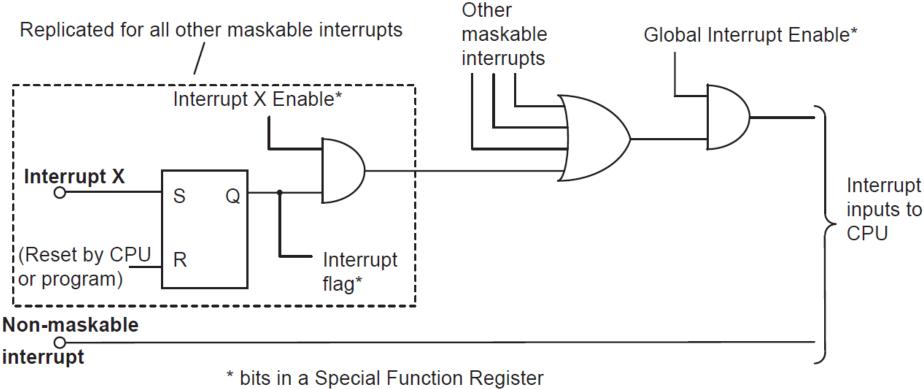

# Interrupt structures

- Microcontrollers have more than one interrupt source generated

- internally and

- externally.

- Assume 'Interrupt X' occurs, sets an S–R bistable and its occurrence is recorded.

- The output of the is called the 'interrupt flag'.

- This is then gated with an enable signal, 'Interrupt X Enable'.

# Other maskable Global Interrupt Enable\* interrupts Interrupt inputs to CPU

# Interrupt structures

enabled interrupt inputs. Any interrupt signal can reach the CPU as long as 'Global Interrupt Enable' is enabled. When the CPU has responded to an interrupt, it is necessary to clear the interrupt flag. The action of disabling an interrupt is sometimes called 'masking'. There are unmaskable which are always external and of the greatest importance Replicated for all other maskable interrupts Interrupt X Enable\* Interrupt X S Q (Reset by CPU R Interrupt or program) flag\* Non-maskable interrupt \* bits in a Special Function Register

If enable is high, then the interrupt signal progresses to an OR gate with other maskable

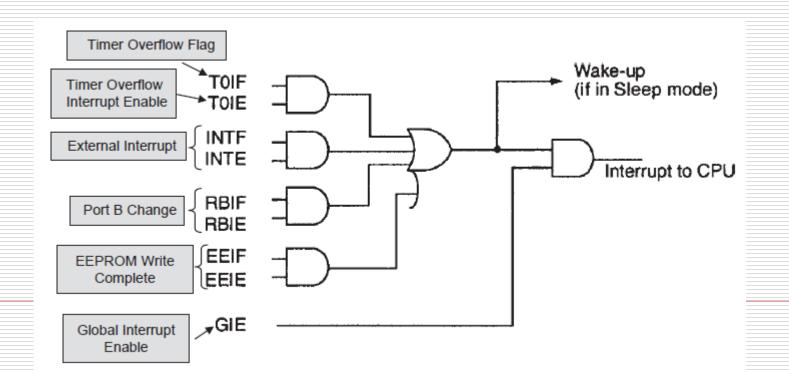

# The 16F84A Interrupt Structure

### **External Interrupt**

This is the only external hardware interrupt input on PIC16F84A. It shares a pin with Port B, bit 0 (pin RB0). It is edge triggered.

#### **Timer Overflow**

This is an interrupt caused by the Timer0 module. It occurs when the timers 8-bit counter overflows. This the software interrupt or internal interrupt.

#### Port B interrupt on change

This interrupt occurs when a change is detected on any of the higher four bits of Port B (RB4,RB5,RB6, and RB7).

#### **EEPROM** write complete

This interrupt occurs when a write instruction to the EEPROM memory is completed (see later lectures).

### Interrupt Logic

- □ The four interrupt sources appear labelled on the left of diagram.

- Each source has an enable line (E) and a flag line (F).

- The INTCON register contains the enable bits for all interrupt sources.

# INTCON REGISTER (ADDRESS 0Bh, 8Bh)

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-x GIE EEIE TOIE INTE RBIE TOIF RBIF INTF bit 7 bit 0 GIE: Global Interrupt Enable bit 1 = Enables all unmasked interrupts o = Disables all interrupts EEIE: EE Write Complete Interrupt Enable bit 1 = Enables the EE Write Complete interrupts o = Disables the EE Write Complete interrupt TOIE: TMR0 Overflow Interrupt Enable bit 1 = Enables the TMR0 interrupt o = Disables the TMR0 interrupt INTE: RB0/INT External Interrupt Enable bit 1 = Enables the RB0/INT external interrupt o = Disables the RB0/INT external interrupt RBIE: RB Port Change Interrupt Enable bit 1 = Enables the RB port change interrupt o = Disables the RB port change interrupt T0IF: TMR0 Overflow Interrupt Flag bit 1 = TMR0 register has overflowed (must be cleared in software) o = TMR0 register did not overflow INTF: RB0/INT External Interrupt Flag bit 1 = The RB0/INT external interrupt occurred (must be cleared in software) o = The RB0/INT external interrupt did not occur **RBIF:** RB Port Change Interrupt Flag bit 1 = At least one of the RB7:RB4 pins changed state (must be cleared in software) 0 = None of the RB7:RB4 pins have changed state Legend:

| R = Readable bit   | W = Writable bit | U = Unimplemented    | ented bit, read as '0' |  |

|--------------------|------------------|----------------------|------------------------|--|

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown     |  |

### REGISTER FILE MAP -PIC16F84A

|   | File Address File Address                                                                                      |                                                 |                                   |            |  |  |  |  |

|---|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------|------------|--|--|--|--|

|   | 00h                                                                                                            | (4) (4)                                         |                                   |            |  |  |  |  |

|   | 01h                                                                                                            | TMR0                                            | OPTION REG                        | 81h        |  |  |  |  |

|   | 02h                                                                                                            | PCL                                             | PCL                               | 82h        |  |  |  |  |

|   | 03h                                                                                                            | STATUS                                          | STATUS                            | 83h        |  |  |  |  |

|   | 04h                                                                                                            | FSR                                             | FSR                               | 84h        |  |  |  |  |

|   | 05h                                                                                                            | PORTA                                           | TRISA                             | 85h        |  |  |  |  |

|   | 06h                                                                                                            | PORTB                                           | TRISB                             | 86h        |  |  |  |  |

| _ | 07h                                                                                                            | _                                               | _                                 | 87h        |  |  |  |  |

| _ | 08h                                                                                                            | EEDATA                                          | EECON1                            | 88h        |  |  |  |  |

|   | 09h                                                                                                            | EEADR                                           | EECON2 <sup>(1)</sup>             | 89h        |  |  |  |  |

|   | 0Ah                                                                                                            | PCLATH                                          | PCLATH                            | 8Ah        |  |  |  |  |

|   | 0Bh                                                                                                            | INTCON                                          | INTCON                            | 8Bh        |  |  |  |  |

|   | 0Ch                                                                                                            |                                                 |                                   | 8Ch        |  |  |  |  |

|   |                                                                                                                | 68<br>General<br>Purpose<br>Registers<br>(SRAM) | Mapped<br>(accesses)<br>in Bank 0 |            |  |  |  |  |

|   |                                                                                                                |                                                 |                                   |            |  |  |  |  |

|   | 4Fh<br>50h                                                                                                     |                                                 |                                   | CFh<br>D0h |  |  |  |  |

|   | nuc                                                                                                            |                                                 |                                   | DUN        |  |  |  |  |

| _ |                                                                                                                |                                                 |                                   |            |  |  |  |  |

|   |                                                                                                                |                                                 |                                   |            |  |  |  |  |

| _ |                                                                                                                |                                                 |                                   | 4          |  |  |  |  |

|   |                                                                                                                |                                                 |                                   | )          |  |  |  |  |

| - | 7Fh                                                                                                            | Bank 0                                          |                                   | FFh        |  |  |  |  |

|   | _                                                                                                              |                                                 | Bank 1                            |            |  |  |  |  |

|   | <ul> <li>Unimplemented data memory location, read as '0'.</li> <li>Note 1: Not a physical register.</li> </ul> |                                                 |                                   |            |  |  |  |  |

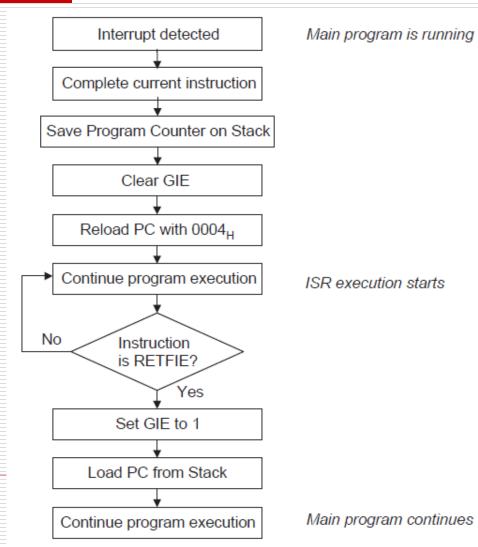

### The CPU Response To An Interrupt

- Assume that an interrupt has occurred, and both its local and the global enable are set.

- CPU executes a special section of program called the Interrupt Service Routine (ISR).

- CPU saves the value of the Program Counter on the top of the Stack to 'know' where to come back to when the ISR is complete.

- To avoid other interrupts possibly interrupting this interrupt, it also clears the Global Interrupt Enable.

- Program Counter is loaded with memory location 0004 as ISR must start at here.

- ISR must end with retfie instruction.

- When this is detected, the CPU sets the GIE to 1, loads the Program Counter from the top of the Stack and then resumes program execution.

- Thus, it returns to the instruction which follows the instruction during which the interrupt was detected.

### Programming With A Single Interrupt

#### For a succesful interrupt application

- Start the ISR at the interrupt vector, location 0004.

- Enable the interrupt that is to be used by setting П the enable bit in the INTCON register.

- Set the Global Enable bit, GIE.

- Clear the interrupt flag within the ISR.

- End the ISR with a retfie instruction.

- Ensure that the interrupt source, for example Port B or Timer 0, is actually set up to generate interrupts.

- The program starts as usual at the reset vector 0000;

#### **Example Program**

- branches over the reset vector to location start, where initialisation takes place.

- Within this we see the GIE and INTE bits being set

- The main program simply outputs the bit patterns 0AH and 15H to Port A

- When an interrupt occurs the interrupt vector address is loaded into the Program Counter, from where program execution continues.

- The first action of the ISR is to jump to location Int Routine. This is placed at program memory location 0080H to give clarity to the simulation.

- The ISR simply clears Port A before clearing its interrupt flag and returning to the main program.

```

;Int Demol

; This program demonstrates simple interrupts.

; Intended for simulation.

```

```

;tjw rev.14.2.09

Tested in simulation 14.9.09

```

```

include p16f84A.inc

; Port A all output

; Port B: bit 0 = Interrupt Input

```

;

;

```

orq

00

start

goto

;here if interrupt occurs

04

orq

Int Routine

goto

0010

orq

;Initialise

start bsf

status,rp0

;select bank 1

movlw

01

;portb bits 1-7 output

movwf trisb

bit 0 is input

movlw

00

movwf trisa

; porta bits all output

;Comment in or out following instruction to change

; interrupt edge

bcf

option reg, intedg

;

status,rp0 ;select bank 0

bcf

intcon, inte ; enable external interrupt

bsf

intcon, gie ; enable global int

bsf

wait

movlw

0a

;set up initial port output values

movwf

porta

nop

15

movlw

movwf

porta

wait

goto

```

```

0080

orq

Int Routine

```

```

movlw 00

```

```

movwf

porta

```

```

bcf

intcon, intf ; clear the interrupt flag

retfie

end

```

# Interrupt Subroutine: General Idea

The interrupt subroutine is called from the program memory location 0004 using a goto instruction org 0x04 goto interrupt subroutine To disable further interrupts during the interrupt subroutine, the interrupt enable flag should be reset bcf INTCON,INTE; (for external interrupt) The interrupt flag should be reset at the end of the subroutine bcf INTCON,INTF; (for external interrupt) The content of the W register and STATUS register should be saved movwf TEMP W; swapf STATUS,0; movwf TEMP S;

### General Structure For An Assembly Program With External Interrupt Subroutine

|        | LIST P=16F84A<br>INCLUDE "P16F84A.INC" |         |          |                             |  |

|--------|----------------------------------------|---------|----------|-----------------------------|--|

|        | ORG                                    | 0X000   | ; addres | s of the main program       |  |

|        | GOTO                                   | START   |          |                             |  |

|        | ORG                                    | 0X004   | ;address | of the ISR                  |  |

|        | GOTO                                   | MY_ISR  |          |                             |  |

| START  |                                        |         |          |                             |  |

|        | BSF                                    | INTCON  | , GIE    | ;global interrupt enable    |  |

|        | BSF                                    | INTCON, | INTE     | ; external interrupt enable |  |

|        |                                        |         |          |                             |  |

| LOOP   |                                        |         |          |                             |  |

| 2001   | GOTO                                   | LOOP    |          |                             |  |

| MY ISR | 0010                                   | 2001    |          |                             |  |

|        | BCF                                    | INTCON, | INTF     | ; clear interrupt flag      |  |

|        |                                        | ,       |          |                             |  |

|        | RETFIE                                 |         |          |                             |  |

|        | END                                    |         |          |                             |  |

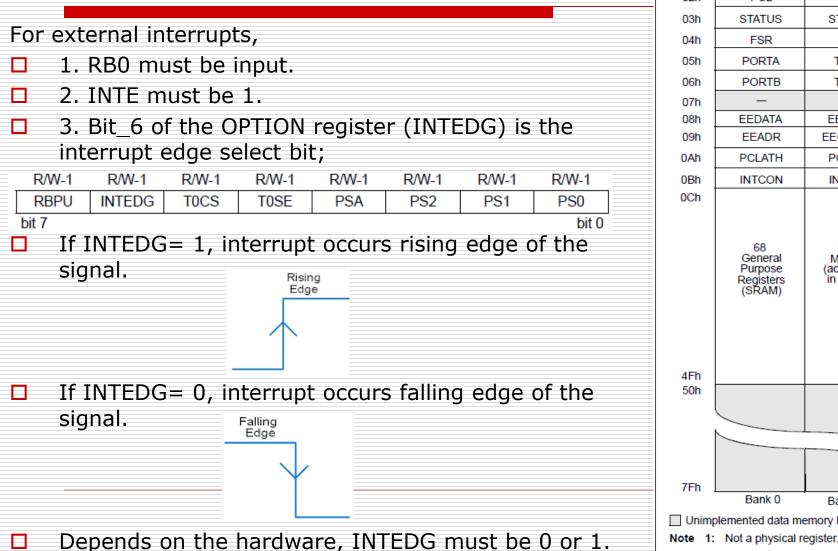

# External interrupts and **OPTION** register

### **REGISTER FILE MAP -PIC16F84A**

| File Address File Address        |                                                 |                                   |            |  |  |  |

|----------------------------------|-------------------------------------------------|-----------------------------------|------------|--|--|--|

| 00h                              | (4) (4)                                         |                                   |            |  |  |  |

| 01h TMR0                         |                                                 | OPTION_REG                        | 81h        |  |  |  |

| 02h                              | PCL                                             | PCL                               | 82h        |  |  |  |

| 03h                              | STATUS                                          | STATUS                            | 83h        |  |  |  |

| 04h                              | FSR                                             | FSR                               | 84h        |  |  |  |

| 05h                              | PORTA                                           | TRISA                             | 85h        |  |  |  |

| 06h                              | PORTB                                           | TRISB                             | 86h        |  |  |  |

| 07h                              | _                                               | _                                 | 87h        |  |  |  |

| 08h                              | EEDATA                                          | EECON1                            | 88h        |  |  |  |

| 09h                              | EEADR                                           | EECON2 <sup>(1)</sup>             | 89h        |  |  |  |

| 0Ah                              | PCLATH                                          | PCLATH                            | 8Ah        |  |  |  |

| 0Bh                              | INTCON                                          | INTCON                            | 8Bh        |  |  |  |

| 0Ch                              |                                                 |                                   | 8Ch        |  |  |  |

|                                  | 68<br>General<br>Purpose<br>Registers<br>(SRAM) | Mapped<br>(accesses)<br>in Bank 0 |            |  |  |  |

| 4Fh                              |                                                 |                                   | CFh        |  |  |  |

| 50h                              |                                                 |                                   | D0h        |  |  |  |

|                                  |                                                 |                                   |            |  |  |  |

|                                  |                                                 |                                   |            |  |  |  |

|                                  |                                                 |                                   | 4          |  |  |  |

|                                  |                                                 |                                   | }          |  |  |  |

| 7Fh                              | Bank 0                                          | Bank 1                            | FFh        |  |  |  |

|                                  |                                                 |                                   | ad ac 101  |  |  |  |

|                                  | plemented data me                               |                                   | au as 'U'. |  |  |  |

| Note 1: Not a physical register. |                                                 |                                   |            |  |  |  |

### swapf

- swapf f,d: swaps the lower nibble and the higher nibble of the content in file register f. In other words, the lower 4 bits are put into the higher 4 bits, and the higher 4 bits are put into the lower 4 bits. Write the result to

- Working register W if d is 0

- File register f if d is 1

### Example

Find the contents of the MYREG register in the following code.

### Solution MYREG EQU 0X20 MOVLW 0X72 ;WREG=72 MOVWF MYREG ;MYREG=72 SWAPF MYREG,F ;MYREG=27

# Protect The Contents Of The Working Register And STATUS Register

# Interrupt subroutine should be written as

|        | ORG h'004'  |               |                        |

|--------|-------------|---------------|------------------------|

|        | GOTO MY ISR |               |                        |

|        | _           |               |                        |

|        |             |               |                        |

| MY_ISR | {           |               |                        |

|        | MOVWF       | SAVE_W        | ; SAVE_W=W_initial     |

|        | SWAPF       | STATUS,W      | ;W=SWAP STATUS_initial |

|        | MOVWF       | SAVE_S ; SAVE | _S=SWAP STATUS_initial |

|        |             |               |                        |

|        | SWAPF       | SAVE_S, W ;W  | =STATUS                |

|        | MOVWF       | STATUS ;STA   | ATUS=STATUS_initial    |

|        | SWAPF       | SAVE_W, F ;W  | =SWAP W_initial        |

|        | SWAPF       | SAVE_W, W ;W  | /=W_initial            |

|        | RETFIE      |               |                        |

# Moving To Multiple Interrupts – Identifying The Source

- 16F84A has four interrupt sources but only one interrupt vector.

- Therefore, if more than one interrupt is enabled, it is not obvious at the beginning of an ISR which interrupt has occurred.

- In this case the programmer must write the ISR so that at its beginning it tests the flags of all possible interrupts and determines from this which one has been called.

interrupt btfsc intcon,0 ;test RBIF goto portb int btfsc intcon,1 ;test external interrupt flag goto ext int btfsc intcon,2 ;test timer overflow flag goto timer int btfsc eecon1,4 ;test EEPROM write complete flag goto eeprom int portb int place portb change ISR here bcf intcon,0 ; and clear the interrupt flag retfie ext int place external interrupt ISR here bcf intcon,1 ; and clear the interrupt flag retfie timer int place timer overflow ISR goes here . . . bcf intcon,2 ; and clear the interrupt flag retfie eeprom int place EEPROM write complete ISR here

bcf eecon1,4 ;and clear the interrupt flag

retfie

# Example: Multiple Interrupts

|       | LIST P=16 | 5F84A         |                           |   | MY_ISR_RB  | D_INT        |                        |

|-------|-----------|---------------|---------------------------|---|------------|--------------|------------------------|

|       | INCLUDE   | "P16F84A.INC" |                           |   | BCF        | INTCON, INTF | ; clear interrupt flag |

|       | ORG       | 0X000 ; addre | ess of the main program   |   | BSF        | PORTB,1      |                        |

|       | GOTO      | START         |                           |   | RET        | FIE          |                        |

|       | ORG       | 0X004 ;addre  | ss of the ISR             |   | MY_ISR_RB  |              |                        |

|       | BTFSC     | INTCON, INTF  |                           |   | BCF        |              | ; clear interrupt flag |

|       | GOTO      | MY_ISR_RB0_IN | Т                         |   | BSF        |              |                        |

|       | BTFSC     | INTCON, RBIF  |                           |   | RET        | FIE          |                        |

|       | GOTO      | MY ISR RB     |                           |   | MY_ISR_TO  |              |                        |

|       | BTFSC     | INTCON,TOIF   |                           |   | BCF        |              | ; clear interrupt flag |

|       | GOTO      | MY_ISR_TO     |                           |   | BSF        | ,            |                        |

|       | GOTO      | MY_ISR_EE     |                           |   | RET        | FIE          |                        |

| START |           |               |                           |   | MY_ISR_EE  |              |                        |

|       | BSF       | INTCON, GIE   | ;global interrupt enable  |   | BSF<br>RET | ,            |                        |

|       | BSF       | INTCON, INTE  | ; external interrupt enab | e | END        |              |                        |

|       | BSF       | INTCON, RBIE  | ;PORTB_change interrup    |   |            | /            |                        |

|       | BSF       | INTCON, TOIE  | ; Timer overflow interrup |   |            |              |                        |

|       | BSF       | INTCON, EEIE  | ;eeprom interrupt enable  |   |            |              |                        |

|       |           | ,             |                           |   |            |              |                        |

| LOOP  |           |               |                           |   |            |              |                        |

|       | GOTO      | LOOP          |                           |   | /          |              |                        |

|       |           |               |                           |   | ,          |              |                        |

|       |           |               |                           |   |            |              |                        |

LIST P=16F84A INCLUDE "P16f84A.INC" \_config \_CP\_OFF&\_WDT\_OFF&\_XT\_OSC org 0x00; goto START org 0x04;Example GOTO ISR ; go to interrupt service routine MAIN PROG CODE ; let linker place main program START BSF STATUS, RP0 CLRF TRISA ; set all PORTA as OUTPUT MOVLW 0xF0 MOVWF TRISB ; buttons attached to RB4 to RB7 BCF STATUS, RP0 ;go to bank 0 MOVLW b'10001000' MOVWF INTCON ;Global interrupt enabled, RB Change interrupt enabled GOTO MAIN :Main routine------MAIN BSF PORTA,0 ;Set RA.0 GOTO MAIN ;Loop ;Interrupt service routine-----ISR BCF INTCON, GIE ; Disable all interrupts inside interrupt service routine BCF PORTA,0 ;clear RA.0 BCF INTCON, RBIF ; Clear external interrupt flag bit BSF INTCON, GIE ; Enable all interrupts on exit GOTO MAIN

END