# MECE336 Microprocessors I Sleep, Watchdog Timer, EEPROM

Dr. Kurtuluş Erinç Akdoğan

kurtuluserinc@cankaya.edu.tr

Course Webpage: http://MECE336.cankaya.edu.tr

#### Sleep

- □ Sleep mode is an important way of saving power.

- □ The microcontroller can be put into this mode by executing the instruction SLEEP.

- SLEEP: Go into standby mode.

- Once in Sleep mode, the microcontroller almost goes into suspended animation.

- The clock oscillator is switched off,

- WDT is cleared,

- program execution is suspended,

- all ports retain their current settings

- PD and TO bits in the Status register are cleared and set respectively.

- If enabled, the WDT continues running.

- Under these conditions, power consumption falls to a negligible amount a typical value of 1 µA, under specific ideal operating conditions.

| off |                  |                                                                                                                                                                                                          |

|-----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | SLEEP            |                                                                                                                                                                                                          |

| d,  | Syntax:          | [ <i>label</i> ] SLEEP                                                                                                                                                                                   |

|     | Operands:        | None                                                                                                                                                                                                     |

|     | Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                               |

|     | Status Affected: | TO, PD                                                                                                                                                                                                   |

| Ð   | Description:     | The power-down status bit, PD is<br>cleared. Time-out status bit, TO<br>is set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. |

| Mnemonic,<br>Operands                                                                                                                  | Description                                                                                                                          | Cycles                        | Status<br>Affected         |  |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------|--|

| BYTE-ORIENTED FILE REGISTER OPERATIONS                                                                                                 |                                                                                                                                      |                               |                            |  |

| ADDWF f, d<br>ANDWF f, d<br>CLRF f<br>CLRW -<br>COMF f, d                                                                              | Add W and f<br>AND W with f<br>Clear f<br>Clear W<br>Complement f                                                                    | 1<br>1<br>1<br>1<br>1         | C,DC,Z<br>Z<br>Z<br>Z<br>Z |  |

| DECF         f, d           DECFSZ         f, d           INCF         f, d           INCFSZ         f, d           IORWF         f, d | Decrement f<br>Decrement f, Skip if 0<br>Increment f<br>Increment f, Skip if 0<br>Inclusive OR W with f                              | 1<br>1 (2)<br>1<br>1 (2)<br>1 | z<br>z<br>z                |  |

| MOVF f, d<br>MOVWF f<br>NOP -<br>RLF f, d                                                                                              | Move f<br>Move W to f<br>No Operation<br>Rotate Left f through Carry                                                                 | 1<br>1<br>1<br>1              | Z                          |  |

| RRF f, d<br>SUBWF f, d<br>SWAPF f, d<br>XORWF f, d                                                                                     | Rotate Right f through Carry<br>Subtract W from f<br>Swap nibbles in f<br>Exclusive OR W with f                                      | 1<br>1<br>1<br>1              | C<br>C,DC,Z<br>Z           |  |

| BIT-ORIEN                                                                                                                              | NTED FILE REGISTER OPERATIONS                                                                                                        |                               |                            |  |

| BCFf, bBSFf, bBTFSCf, bBTFSSf, b                                                                                                       | Bit Clear f<br>Bit Set f<br>Bit Test f, Skip if Clear<br>Bit Test f, Skip if Set                                                     | 1<br>1<br>1 (2)<br>1 (2)      |                            |  |

| ADDLW k<br>ANDLW k<br>CALL k<br>CLRWDT -                                                                                               | L AND CONTROL OPERATIONS<br>Add literal and W<br>AND literal with W<br>Call subroutine<br>Clear Watchdog Timer                       | 1<br>1<br>2<br>1              | C,DC,Z<br>Z<br>TO,PD       |  |

| GOTO k<br>IORLW k<br>MOVLW k<br>RETFIE -                                                                                               | Go to address<br>Inclusive OR literal with W<br>Move literal to W<br>Return from interrupt                                           | 2<br>1<br>1<br>2              | Z                          |  |

| <br>RETLW k<br>RETURN -<br>SLEEP -<br>SUBLW k<br>XORLW k                                                                               | Return with literal in W<br>Return from Subroutine<br>Go into standby mode<br>Subtract W from literal<br>Exclusive OR literal with W | 2<br>2<br>1<br>1<br>1         | TO,PD<br>C,DC,Z<br>Z       |  |

\_

## Status Register

|         | R/W-0       | R/W-0                                                                                                                                                                                     | R/W-0          | R-1           | R-1             | R/W-x | R/W-x        | R/W-x      |

|---------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|-----------------|-------|--------------|------------|

|         | IRP         | RP1                                                                                                                                                                                       | RP0            | TO            | PD              | Z     | DC           | С          |

|         | bit 7       |                                                                                                                                                                                           |                |               |                 |       |              | bit 0      |

|         |             |                                                                                                                                                                                           |                |               |                 |       |              |            |

| bit 7-6 | Unimplem    | ented: Mair                                                                                                                                                                               | ntain as '0'   |               |                 |       |              |            |

| bit 5   | RP0: Regi   | ster Bank Se                                                                                                                                                                              | elect bits (us | ed for direct | addressing      | )     |              |            |

|         |             | 1 (80h - FF                                                                                                                                                                               | *              |               |                 |       |              |            |

|         | _           | 0 (00h - 7Fi                                                                                                                                                                              | n)             |               |                 |       |              |            |

| bit 4   | TO: Time-o  |                                                                                                                                                                                           | numm in also   | ation on an   | nnn instruct    |       |              |            |

|         |             | oower-up, CI<br>T time-out o                                                                                                                                                              |                | ction, or SL  | EEP Instruct    | ion   |              |            |

| bit 3   | PD: Power   |                                                                                                                                                                                           | oounou         |               |                 |       |              |            |

| Dit C   |             | power-up or                                                                                                                                                                               | by the CLRW    | DT instructio | on              |       |              |            |

|         |             | ecution of th                                                                                                                                                                             | -              |               |                 |       |              |            |

| bit 2   | Z: Zero bit |                                                                                                                                                                                           |                |               |                 |       |              |            |

|         |             | esult of an ar                                                                                                                                                                            |                | ~ .           |                 |       |              |            |

|         |             | esult of an ar                                                                                                                                                                            |                | • •           |                 |       |              |            |

| bit 1   |             | DC: Digit Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow, the polarity is reversed)                                                                               |                |               |                 |       |              |            |

|         |             | 1 = A carry-out from the 4th low order bit of the result occurred                                                                                                                         |                |               |                 |       |              |            |

|         | _           | 0 = No carry-out from the 4th low order bit of the result                                                                                                                                 |                |               |                 |       |              |            |

| bit 0   |             | C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow, the polarity is reversed) <ol> <li>A carry-out from the Most Significant Bit of the result occurred</li> </ol> |                |               |                 |       |              |            |

|         | ,           |                                                                                                                                                                                           |                |               |                 |       |              |            |

|         |             | rry-out from                                                                                                                                                                              | ~              |               |                 |       |              |            |

|         | Note:       |                                                                                                                                                                                           |                |               | the twos c      |       | of the secon | d operand. |

|         |             |                                                                                                                                                                                           |                |               | his bit is load |       |              |            |

|         |             | bit of the so                                                                                                                                                                             | ource registe  | r.            |                 |       | -            |            |

## Sleep: Awakening

External reset through MCLR pin. While this causes a wake-up, it also resets the microcontroller; therefore, its use seems limited to complete program restarts. It is possible, however, to detect that the microcontroller has just been in Sleep mode, due to the state of the PD pin in the Status register.

## Sleep: Awakening

- WDT wake-up. WDT is blocked from causing a reset when in Sleep. Instead, on overflow it just causes a wake-up from Sleep, and the microcontroller continues program execution from the instruction following the Sleep mode.

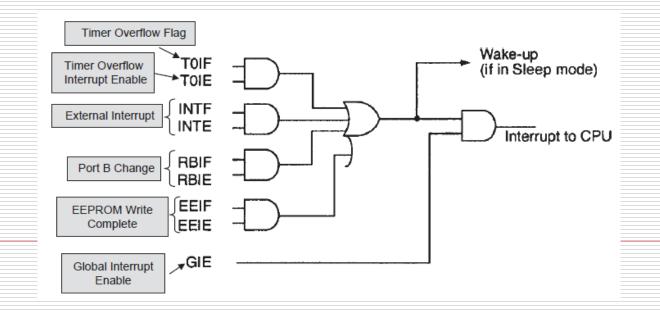

- Occurrence of interrupt. If any interrupt was enabled prior to going into SLEEP, upon receipt of interrupt input, wake-up from Sleep occurs regardless of the state of the Global Interrupt Enable. Timer 0 cannot, however, generate an interrupt, as the internal clock is disabled.

#### Example

- Write a program that counts the number of positive transitions on input RB.0/INT and displays the current "count" on four LEDs on outputs RB.4 - RB.7.

- Note that the INTEDG bit in the OPTION\_REG may be set such that the external interrupt occurs on the positive edge of a signal on RB.0

## INTCON REGISTER (ADDRESS 0Bh, 8Bh)

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-x GIE EEIE TOIE INTE RBIE TOIF RBIF INTF bit 7 bit 0 GIE: Global Interrupt Enable bit 1 = Enables all unmasked interrupts o = Disables all interrupts EEIE: EE Write Complete Interrupt Enable bit 1 = Enables the EE Write Complete interrupts o = Disables the EE Write Complete interrupt TOIE: TMR0 Overflow Interrupt Enable bit 1 = Enables the TMR0 interrupt o = Disables the TMR0 interrupt INTE: RB0/INT External Interrupt Enable bit 1 = Enables the RB0/INT external interrupt o = Disables the RB0/INT external interrupt RBIE: RB Port Change Interrupt Enable bit 1 = Enables the RB port change interrupt o = Disables the RB port change interrupt T0IF: TMR0 Overflow Interrupt Flag bit 1 = TMR0 register has overflowed (must be cleared in software) o = TMR0 register did not overflow INTF: RB0/INT External Interrupt Flag bit 1 = The RB0/INT external interrupt occurred (must be cleared in software) o = The RB0/INT external interrupt did not occur **RBIF:** RB Port Change Interrupt Flag bit 1 = At least one of the RB7:RB4 pins changed state (must be cleared in software) 0 = None of the RB7:RB4 pins have changed state Legend:

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

|--------------------|------------------|----------------------|--------------------|

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

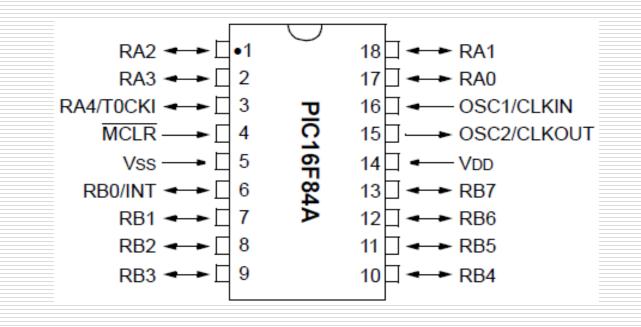

#### REGISTER FILE MAP -PIC16F84A

|   | File Addre                                                                                                     | ss                                              | F                                 | ile Address |  |  |

|---|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------|-------------|--|--|

|   | 00h                                                                                                            | Indirect addr. <sup>(1)</sup>                   | Indirect addr. <sup>(1)</sup>     | 80h         |  |  |

|   | 01h                                                                                                            | TMR0                                            | OPTION REG                        | 81h         |  |  |

|   | 02h                                                                                                            | PCL                                             | PCL                               | 82h         |  |  |

|   | 03h                                                                                                            | STATUS                                          | STATUS                            | 83h         |  |  |

|   | 04h                                                                                                            | FSR                                             | FSR                               | 84h         |  |  |

|   | 05h                                                                                                            | PORTA                                           | TRISA                             | 85h         |  |  |

|   | 06h                                                                                                            | PORTB                                           | TRISB                             | 86h         |  |  |

|   | 07h                                                                                                            | _                                               | _                                 | 87h         |  |  |

| _ | 08h                                                                                                            | EEDATA                                          | EECON1                            | 88h         |  |  |

|   | 09h                                                                                                            | EEADR                                           | EECON2 <sup>(1)</sup>             | 89h         |  |  |

|   | 0Ah                                                                                                            | PCLATH                                          | PCLATH                            | 8Ah         |  |  |

| _ | 0Bh                                                                                                            | INTCON                                          | INTCON                            | 8Bh         |  |  |

|   | 0Ch                                                                                                            |                                                 |                                   | 8Ch         |  |  |

|   |                                                                                                                | 68<br>General<br>Purpose<br>Registers<br>(SRAM) | Mapped<br>(accesses)<br>in Bank 0 |             |  |  |

|   |                                                                                                                |                                                 |                                   |             |  |  |

|   | 4Fh<br>50h                                                                                                     |                                                 |                                   | CFh<br>D0h  |  |  |

|   | nuc                                                                                                            |                                                 |                                   | DUN         |  |  |

| _ |                                                                                                                |                                                 |                                   |             |  |  |

| _ |                                                                                                                |                                                 |                                   |             |  |  |

|   |                                                                                                                |                                                 |                                   | ۱<br>۱      |  |  |

|   |                                                                                                                |                                                 |                                   |             |  |  |

| - | 7Fh                                                                                                            | Bank 0                                          |                                   | FFh         |  |  |

|   | _                                                                                                              |                                                 | Bank 1                            |             |  |  |

|   | <ul> <li>Unimplemented data memory location, read as '0'.</li> <li>Note 1: Not a physical register.</li> </ul> |                                                 |                                   |             |  |  |

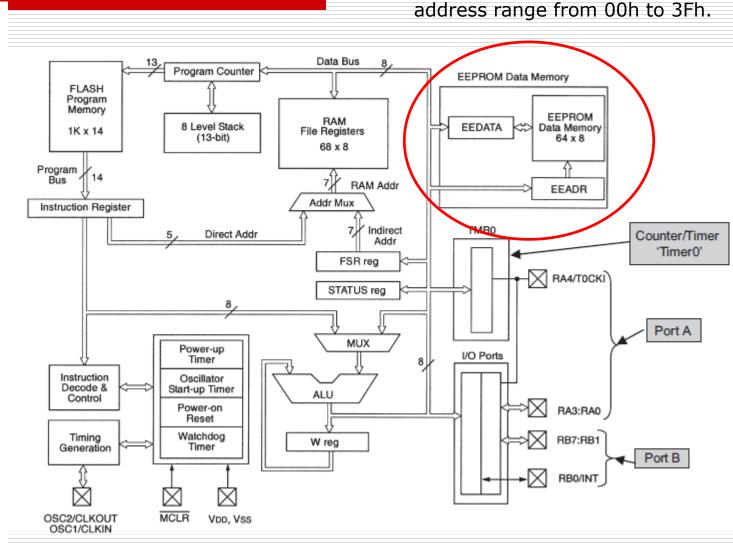

## External interrupts and **OPTION** register

#### **REGISTER FILE MAP -PIC16F84A**

| File Address File Address        |                                                 |                                   |            |  |  |  |  |

|----------------------------------|-------------------------------------------------|-----------------------------------|------------|--|--|--|--|

| 00h                              | Indirect addr. <sup>(1)</sup>                   | Indirect addr. <sup>(1)</sup>     | 80h        |  |  |  |  |

| 01h                              | TMR0                                            | OPTION_REG                        | 81h        |  |  |  |  |

| 02h                              | PCL                                             | PCL                               | 82h        |  |  |  |  |

| 03h                              | STATUS                                          | STATUS                            | 83h        |  |  |  |  |

| 04h                              | FSR                                             | FSR                               | 84h        |  |  |  |  |

| 05h                              | PORTA                                           | TRISA                             | 85h        |  |  |  |  |

| 06h                              | PORTB                                           | TRISB                             | 86h        |  |  |  |  |

| 07h                              | _                                               | _                                 | 87h        |  |  |  |  |

| 08h                              | EEDATA                                          | EECON1                            | 88h        |  |  |  |  |

| 09h                              | EEADR                                           | EECON2 <sup>(1)</sup>             | 89h        |  |  |  |  |

| 0Ah                              | PCLATH                                          | PCLATH                            | 8Ah        |  |  |  |  |

| 0Bh                              | INTCON                                          | INTCON                            | 8Bh        |  |  |  |  |

| 0Ch                              |                                                 |                                   | 8Ch        |  |  |  |  |

|                                  | 68<br>General<br>Purpose<br>Registers<br>(SRAM) | Mapped<br>(accesses)<br>in Bank 0 |            |  |  |  |  |

| 4Fh                              |                                                 |                                   | CFh        |  |  |  |  |

| 50h                              |                                                 |                                   | D0h        |  |  |  |  |

|                                  |                                                 |                                   |            |  |  |  |  |

|                                  |                                                 |                                   |            |  |  |  |  |

|                                  |                                                 |                                   | 4          |  |  |  |  |

|                                  |                                                 |                                   | }          |  |  |  |  |

| 7Fh                              | Bank 0                                          | Bank 4                            | FFh        |  |  |  |  |

|                                  | Bank 0 Bank 1                                   |                                   |            |  |  |  |  |

|                                  |                                                 |                                   | au as '0'. |  |  |  |  |

| Note 1: Not a physical register. |                                                 |                                   |            |  |  |  |  |

| LIST P=16F84A                           |                  |                        |

|-----------------------------------------|------------------|------------------------|

| INCLUDE "P16f84A.INC"                   | PT1: SLEEP       |                        |

| CONFIGCP_OFF&_WDT_OFF&_XT_OSC           | GOTO PT1         |                        |

|                                         | INT_SERV:        |                        |

| ORG 00                                  | INCF COUNTER, F  |                        |

| GOTO MAIN                               |                  |                        |

|                                         | BTFSS COUNTER, 0 | ; light the            |

| ORG 04                                  |                  | ; appropriate LEDs     |

| GOTO INT SERV                           | BCF PORTB, 4     |                        |

|                                         | BTFSC COUNTER, 0 |                        |

| MAIN:                                   | BSF PORTB, 4     |                        |

| BSF STATUS, RPO ; bank 1                | BTFSS COUNTER, 1 |                        |

| MOVLW 1                                 | BCF PORTB, 5     |                        |

| MOVWF TRISB                             | BTFSC COUNTER, 1 |                        |

| BCF STATUS, RPO ; back to bank 0        | BSF PORTB, 5     |                        |

|                                         | BTFSS COUNTER, 2 |                        |

| COUNTER EQU 20                          | BCF PORTB, 6     |                        |

| CLRF COUNTER ; zero the counter         | BTFSC COUNTER, 2 |                        |

| BCF PORTB, 4 ; zero the LEDs            | BSF PORTB, 6     |                        |

| BCF PORTB, 5                            | BTFSS COUNTER, 3 |                        |

| BCF PORTB, 6                            | BCF PORTB, 7     |                        |

| BCF PORTB, 7                            | BTFSC COUNTER, 3 |                        |

|                                         | BSF PORTB, 7     |                        |

| BSF OPTION REG, INTEDG ; interrupt on   |                  |                        |

| _ ; positive                            | BCF INTCON, INTF | ; clear the            |

| BCF INTCON, INTF ; clear interrupt flag |                  | ; appropriate flag     |

| BSF INTCON, INTE ; mask for external    | RETFIE           | ; this also set global |

| ; interrupts                            |                  | ; interrupt enable     |

| BSF INTCON, GIE ; enable interrupts     |                  |                        |

| ↓                                       | END              |                        |

|                                         |                  |                        |

https://phanderson.com/PIC/16C84/interrupts/interrupt\_1.html

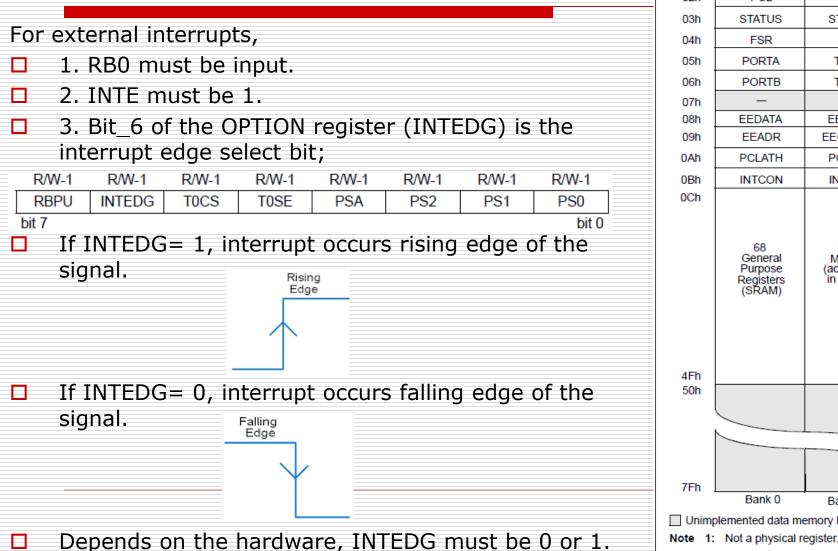

#### **EEPROM:** Basics

- The EEPROM is nonvolatile and is particularly useful for holding data variables that can be changed but are likely to be needed for the medium to long term.

- Examples include TV tuner settings, phone numbers stored in a cell phone or calibration settings on a measuring instrument.

- In the 16F84A ,the EEPROM is not placed in the main data memory map. Instead it is addressed through the EEADR register and data is transferred through EEDATA register. These are both SFRs

PIC16F84A devices have 64

bytes of data EEPROM with an

|            | REGISTER                                        | R FILE MAP                        |             |

|------------|-------------------------------------------------|-----------------------------------|-------------|

| Addre      | ss                                              | F                                 | ile Address |

| 00h        | Indirect addr. <sup>(1)</sup>                   | Indirect addr. <sup>(1)</sup>     | 80h         |

| 01h        | TMR0                                            | OPTION_REG                        | 81h         |

| 02h        | PCL                                             | PCL                               | 82h         |

| 03h        | STATUS                                          | STATUS                            | 83h         |

| 04h        | FSR                                             | FSR                               | 84h         |

| 05h        | PORTA                                           | TRISA                             | 85h         |

| 06h        | PORTB                                           | TRISB                             | 86h         |

| 07h        | _                                               | —                                 | 87h         |

| 08h        | EEDATA                                          | EECON1                            | 88h         |

| 09h        | EEADR                                           | EECON2 <sup>(1)</sup>             | 89h         |

| 0Ah        | PCLATH                                          | PCLATH                            | 8Ah         |

| 0Bh        | INTCON                                          | INTCON                            | 8Bh         |

| 4Fh        | 68<br>General<br>Purpose<br>Registers<br>(SRAM) | Mapped<br>(accesses)<br>in Bank 0 | CFh         |

| 4Fn<br>50h |                                                 |                                   | DOh         |

| 7Fh        | Pank 0                                          |                                   | FFh         |

|            | Bank 0                                          | Bank 1                            |             |

File

- The EEPROM data memory allows byte read and write. A byte write automatically erases the location and writes the new data (erase before write).

- EEPROM is addressed through the EEADR register and data is transferred through the EEDATA register.

- Reading from EEPROM is a simple process but writing to it is not. The latter takes significant time in electronic terms (i.e. milliseconds) and care must be taken to avoid accidental writes. A set of controls is therefore required to start the process and (for write) to detect when it is ended.

- □ These are found in the bits of the EECON1 register;

- To read an EEPROM location, the required address must be placed in EEADR and the RD bit set in EECON1.

- □ The data in that memory location is then copied to the EEDATA register and can be read immediately.

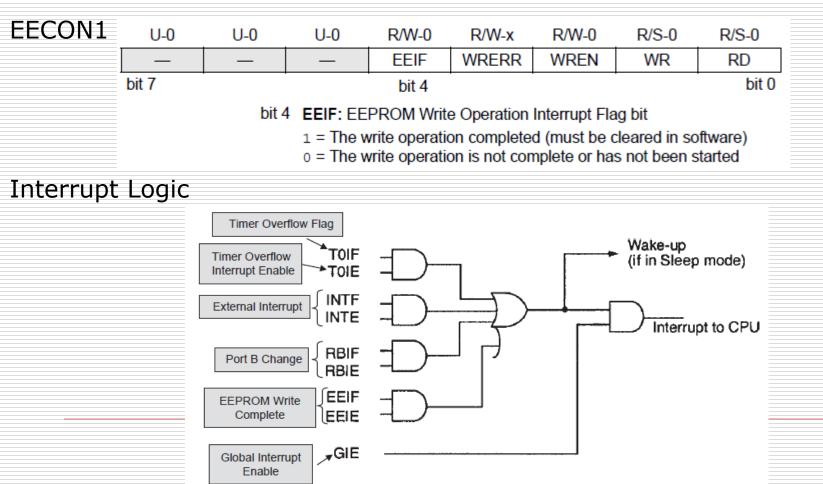

#### EECON1

| REGISTER 3-1: | EECON1 F                                                                                                                                                                                                                                                                      | REGISTER       | (ADDRES       | S 88h)        |               |              |              |          |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|---------------|---------------|--------------|--------------|----------|

|               | U-0                                                                                                                                                                                                                                                                           | U-0            | U-0           | R/W-0         | R/W-x         | R/W-0        | R/S-0        | R/S-0    |

|               | —                                                                                                                                                                                                                                                                             | —              | —             | EEIF          | WRERR         | WREN         | WR           | RD       |

|               | bit 7                                                                                                                                                                                                                                                                         |                |               |               |               |              |              | bit 0    |

| L# 7 5        |                                                                                                                                                                                                                                                                               | ente de De e   | d a a 101     |               |               |              |              |          |

| bit 7-5       | Unimplem                                                                                                                                                                                                                                                                      | ented: Rea     | d as 0        |               |               |              |              |          |

| bit 4         | EEIF: EEP                                                                                                                                                                                                                                                                     | ROM Write      | Operation In  | terrupt Flag  | bit           |              |              |          |

|               |                                                                                                                                                                                                                                                                               |                |               | •             | eared in soft |              |              |          |

|               | 0 = The wr                                                                                                                                                                                                                                                                    | ite operatior  | n is not comp | plete or has  | not been sta  | rted         |              |          |

| bit 3         | WRERR: E                                                                                                                                                                                                                                                                      | EPROM Er       | ror Flag bit  |               |               |              |              |          |

|               | 1 = A write                                                                                                                                                                                                                                                                   | operation is   | prematurel    | y terminated  | 1             |              |              |          |

|               |                                                                                                                                                                                                                                                                               |                | -             | Reset durin   | g normal op   | eration)     |              |          |

|               | 0 = The wr                                                                                                                                                                                                                                                                    | ite operatior  | n completed   |               |               |              |              |          |

| bit 2         | WREN: EE                                                                                                                                                                                                                                                                      | PROM Writ      | e Enable bit  |               |               |              |              |          |

|               | 1 = Allows                                                                                                                                                                                                                                                                    | write cycles   |               |               |               |              |              |          |

|               | o = Inhibits                                                                                                                                                                                                                                                                  | write to the   | EEPROM        |               |               |              |              |          |

| bit 1         | <ul> <li>WR: Write Control bit</li> <li>1 = Initiates a write cycle. The bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.</li> <li>0 = Write cycle to the EEPROM is complete</li> <li>RD: Read Control bit</li> </ul> |                |               |               |               |              |              |          |

|               |                                                                                                                                                                                                                                                                               |                |               |               |               | ne WR bit    |              |          |

|               |                                                                                                                                                                                                                                                                               |                |               |               |               |              |              |          |

|               |                                                                                                                                                                                                                                                                               |                |               |               |               |              |              |          |

| bit 0         |                                                                                                                                                                                                                                                                               |                |               |               |               |              |              |          |

|               |                                                                                                                                                                                                                                                                               |                |               | is cleared ir | hardware.     | The RD bit o | an only be s | set (not |

|               |                                                                                                                                                                                                                                                                               | ) in software  |               |               |               |              |              |          |

|               | 0 = Does n                                                                                                                                                                                                                                                                    | ot initiate ar | EEPROM I      | read          |               |              |              |          |

#### Reading the EEPROM Data Memory

To read a data memory location, the user must write the address to the EEADR register and then set control bit RD (EECON1<0>). The data is available, in the very next cycle, in the EEDATA register; therefore, it can be read in the next instruction. EEDATA will hold this value until another read or until it is written to by the user (during a write operation).

| BCF   | STATUS, RP0 | ; Bank 0          |

|-------|-------------|-------------------|

| MOVLW | CONFIG_ADDR | • • •             |

| MOVWF | EEADR       | ; Address to read |

| BSF   | STATUS, RP0 | ; Bank 1          |

| BSF   | EECON1, RD  | ; EE Read         |

| BCF   | STATUS, RP0 | ; Bank 0          |

| MOVF  | EEDATA, W   | ; $W = EEDATA$    |

| MOVWF | PORTB       | ; PORTB = EEDATA  |

|       |             |                   |

# Writing to the EEPROM Data Memory

**REGISTER FILE MAP**

| File Address File Address |                                                 |                                   |            |  |  |

|---------------------------|-------------------------------------------------|-----------------------------------|------------|--|--|

| 00h                       | Indirect addr. <sup>(1)</sup>                   | Indirect addr. <sup>(1)</sup>     | 80h        |  |  |

| 01h                       | TMR0                                            | OPTION_REG                        | 81h        |  |  |

| 02h                       | PCL                                             | PCL                               | 82h        |  |  |

| 03h                       | STATUS                                          | STATUS                            | 83h        |  |  |

| 04h                       | FSR                                             | FSR                               | 84h        |  |  |

| 05h                       | PORTA                                           | TRISA                             | 85h        |  |  |

| 06h                       | PORTB                                           | TRISB                             | 86h        |  |  |

| 07h                       | —                                               | —                                 | 87h        |  |  |

| 08h                       | EEDATA                                          | EECON1                            | 88h        |  |  |

| 09h                       | EEADR                                           | EECON2 <sup>(1)</sup>             | 89h        |  |  |

| 0Ah                       | PCLATH                                          | PCLATH                            | 8Ah        |  |  |

| 0Bh                       | INTCON                                          | INTCON                            | 8Bh        |  |  |

| 0Ch                       | 68<br>General<br>Purpose<br>Registers<br>(SRAM) | Mapped<br>(accesses)<br>in Bank 0 | 8Ch        |  |  |

| 4Fh<br>50h                |                                                 |                                   | CFh<br>D0h |  |  |

| 7Fh                       |                                                 |                                   | FFh        |  |  |

|                           | Bank 0                                          | Bank 1                            |            |  |  |

- To write to an EEPROM location, the required data and address must be placed in EEDATA and EEADR respectively.

- The write process is enabled by the WREN (Write Enable) bit being set high, followed by the bytes 55H followed by AAH being sent to the EECON2 register.

- The built-in requirement for these codes helps to ensure that accidental writes do not take place, for example on power-up or -down.

- The WR bit is then set high and writing actually commences.

- The write completion is signalled by the setting of bit EEIF in EECON1.

- EECON2 is not a physical register.

#### Writing to the EEPROM Data Memory

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDATA register. Then the user must follow a specific sequence to initiate the write for each byte.

| BSF   | STATUS, RPO  | ; Bank 1                 |

|-------|--------------|--------------------------|

| BCF   | INTCON, GIE  | ; Disable INTs.          |

| BSF   | EECON1, WREN | ; Enable Write           |

| MOVLW | 55h ;        |                          |

| MOVWF | EECON2       | ; Write 55h              |

| MOVLW | AAh ;        |                          |

| MOVWF | EECON2       | ; Write AAh              |

| BSF   | EECON1,WR    | ; Set WR bit begin write |

| BSF   | INTCON, GIE  | ; Enable INTs            |

The write will not initiate if the above sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. We strongly recommend that interrupts be disabled during this code segment.

#### Writing to the EEPROM Data Memory

WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM. The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

| BSF   | STATUS, RPO  | ; Bank 1                 |

|-------|--------------|--------------------------|

| BCF   | INTCON, GIE  | ; Disable INTs.          |

| BSF   | EECON1, WREN | ; Enable Write           |

| MOVLW | 55h ;        |                          |

| MOVWF | EECON2       | ; Write 55h              |

| MOVLW | AAh ;        |                          |

| MOVWF | EECON2       | ; Write AAh              |

| BSF   | EECON1,WR    | ; Set WR bit begin write |

| BSF   | INTCON, GIE  | ; Enable INTs            |

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

#### Example

#### □ Write h'E3' to location 0X03 of EEPROM.

| MOVLW | 0X03         |                          |

|-------|--------------|--------------------------|

| MOVWF | EEADR        |                          |

| MOVLW | h'E3'        |                          |

| MOVWF | EEDATA       |                          |

| BSF   | STATUS, RPO  | ; Bank 1                 |

| BCF   | INTCON, GIE  | ; Disable INTs.          |

| BSF   | EECON1, WREN | ; Enable Write           |

| MOVLW | 55h ;        |                          |

| MOVWF | EECON2       | ; Write 55h              |

| MOVLW | AAh ;        |                          |

| MOVWF | EECON2       | ; Write AAh              |

| BSF   | EECON1,WR    | ; Set WR bit begin write |

| BSF   | INTCON, GIE  | ; Enable INTs            |

|       |              |                          |

#### DATA EEPROM INTERRUPT

□ At the completion of a data EEPROM write cycle, flag bit EEIF (EECON1<4>) will be set. The interrupt can be enabled/disabled by setting/clearing enable bit EEIE (INTCON<6>)

## INTCON REGISTER (ADDRESS 0Bh, 8Bh)

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-x GIE EEIE TOIE INTE RBIE TOIF RBIF INTF bit 7 bit 0 GIE: Global Interrupt Enable bit 1 = Enables all unmasked interrupts o = Disables all interrupts EEIE: EE Write Complete Interrupt Enable bit 1 = Enables the EE Write Complete interrupts o = Disables the EE Write Complete interrupt TOIE: TMR0 Overflow Interrupt Enable bit 1 = Enables the TMR0 interrupt o = Disables the TMR0 interrupt INTE: RB0/INT External Interrupt Enable bit 1 = Enables the RB0/INT external interrupt o = Disables the RB0/INT external interrupt RBIE: RB Port Change Interrupt Enable bit 1 = Enables the RB port change interrupt o = Disables the RB port change interrupt T0IF: TMR0 Overflow Interrupt Flag bit 1 = TMR0 register has overflowed (must be cleared in software) o = TMR0 register did not overflow INTF: RB0/INT External Interrupt Flag bit 1 = The RB0/INT external interrupt occurred (must be cleared in software) o = The RB0/INT external interrupt did not occur **RBIF:** RB Port Change Interrupt Flag bit 1 = At least one of the RB7:RB4 pins changed state (must be cleared in software) 0 = None of the RB7:RB4 pins have changed state Legend:

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|--------------------|------------------|------------------------------------|--------------------|--|--|

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### REGISTER FILE MAP -PIC16F84A

|   | File Addre                                                                                                     | ss                                              | F                                 | ile Address |  |  |  |

|---|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------|-------------|--|--|--|

|   | 00h                                                                                                            | Indirect addr. <sup>(1)</sup>                   | Indirect addr. <sup>(1)</sup>     | 80h         |  |  |  |

|   | 01h                                                                                                            | TMR0                                            | OPTION REG                        | 81h         |  |  |  |

|   | 02h                                                                                                            | PCL                                             | PCL                               | 82h         |  |  |  |

|   | 03h                                                                                                            | STATUS                                          | STATUS                            | 83h         |  |  |  |

|   | 04h                                                                                                            | FSR                                             | FSR                               | 84h         |  |  |  |

|   | 05h                                                                                                            | PORTA                                           | TRISA                             | 85h         |  |  |  |

|   | 06h                                                                                                            | PORTB                                           | TRISB                             | 86h         |  |  |  |

|   | 07h                                                                                                            | _                                               | _                                 | 87h         |  |  |  |

| _ | 08h                                                                                                            | EEDATA                                          | EECON1                            | 88h         |  |  |  |

|   | 09h                                                                                                            | EEADR                                           | EECON2 <sup>(1)</sup>             | 89h         |  |  |  |

|   | 0Ah                                                                                                            | PCLATH                                          | PCLATH                            | 8Ah         |  |  |  |

|   | 0Bh                                                                                                            | INTCON                                          | INTCON                            | 8Bh         |  |  |  |

| _ | 0Ch                                                                                                            |                                                 |                                   | 8Ch         |  |  |  |

|   |                                                                                                                | 68<br>General<br>Purpose<br>Registers<br>(SRAM) | Mapped<br>(accesses)<br>in Bank 0 |             |  |  |  |

|   |                                                                                                                |                                                 |                                   |             |  |  |  |

|   | 4Fh<br>50h                                                                                                     |                                                 |                                   | CFh<br>D0h  |  |  |  |

|   | nuc                                                                                                            |                                                 |                                   | DUN         |  |  |  |

| _ |                                                                                                                |                                                 |                                   |             |  |  |  |

|   |                                                                                                                |                                                 |                                   |             |  |  |  |

| _ |                                                                                                                |                                                 |                                   | 4           |  |  |  |

|   |                                                                                                                |                                                 |                                   |             |  |  |  |

| - | 7Fh                                                                                                            | Bank 0                                          |                                   | FFh         |  |  |  |

|   | _                                                                                                              |                                                 | Bank 1                            |             |  |  |  |

|   | <ul> <li>Unimplemented data memory location, read as '0'.</li> <li>Note 1: Not a physical register.</li> </ul> |                                                 |                                   |             |  |  |  |

| Example: What                                                                          | does this                                            |

|----------------------------------------------------------------------------------------|------------------------------------------------------|

| program do?                                                                            | movlw 0xAA;<br>movwf EECON2;                         |

| list p=16f84a;<br>include "p16f84a.inc"                                                | bsf EECON1,WR;<br>bcf STATUS,RP0;<br>bsf INTCON,GIE; |

| address1equ0x00; EEPROM address 1readAddress equ0x23; EEPROM address readvalue1equ.12; | wait_write1<br>btfss PORTB,0;<br>goto wait_write1;   |

| org 0;                                                                                 | ; Read from EEPROM                                   |

| goto main;                                                                             | movlw readAddress;                                   |

| org 0x04;                                                                              | movwf EEADR;                                         |

| goto eeprom_isr;                                                                       | bsf STATUS,RP0;                                      |

| main;                                                                                  | bsi STATUS,RPU,                                      |

| bsf STATUS,RP0;                                                                        | bcf EECON1,WREN;                                     |

| clrf TRISB;                                                                            | bsf EECON1,RD;                                       |

| bcf STATUS,RP0;                                                                        | bcf STATUS,RP0;                                      |

| clrf PORTB;                                                                            | movf EEDATA,0;                                       |

| movlw address1;                                                                        | loop;                                                |

| movwf EEADR;                                                                           | goto loop;                                           |

| movlw value1;                                                                          | eeprom_isr                                           |

| movwf EEDATA;                                                                          | bsf   PORTB,0;                                       |

| bsf STATUS,RP0;                                                                        | bsf STATUS,RP0;                                      |

| bcf INTCON,GIE;                                                                        | bcf EECON1,EEIF;                                     |

| bsf INTCON,EEIE;                                                                       | bcf STATUS,RP0;                                      |

| bsf EECON1,WREN;                                                                       | retfie;                                              |

| movlw 0x55;<br>movwf EECON2;                                                           | end                                                  |

## The Watchdog Timer

- The primary function of the Watchdog Timer (WDT) is

- to reset the microcontroller, in the event of a software malfunction, by resetting the device if it has not been cleared in software.

- to wake the device from Sleep mode.

- The Watchdog Timer is a free running On-Chip RC Oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin.

- That means that the WDT will run even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

- During normal operation, a WDT time-out generates a device RESET.

- □ If the device is in SLEEP mode, a WDT wake-up causes the device to wake-up and continue with normal operation.

- The WDT can be enabled by programming configuration bit WDTE as a '1' by using the relevant coniguration bit

\_\_\_config \_CP\_OFF&\_WDT\_ON&\_XT\_OSC

|                                                              | R/P-u     | R/P-u     | R/P-u         | R/P-u      | R/P-u |  |

|--------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-----------|-----------|---------------|------------|-------|--|

|                                                              | CP        | PWRTE     | WDTE          | F0SC1      | F0SC0 |  |

|                                                              | bit13 |       |       |       |       |       |       |       |       |           |           | bit 2         |            | bit0  |  |

| PIC16F84A CONFIGURATION WORD WDTE: Watchdog Timer Enable bit |       |       |       |       |       |       |       |       |       | nable bit |           |               |            |       |  |

|                                                              |       |       |       |       |       |       |       |       |       | 1 = WD    | )T enable | d             |            |       |  |

|                                                              |       |       |       |       |       |       |       |       |       |           |           | $0 = W\Gamma$ | )T disable | d     |  |

#### WDT OPERATION

- □ When enabled, the WDT will increment until it overflows or "times out".

- □ A WDT time-out will force a device Reset, except during Sleep modes.

- To prevent a WDT Time-out Reset, the user must periodically clear the Watchdog Timer using the instructions, CLRWDT.

- If the WDT times out during Sleep modes, the device will wake-up and continue code execution from where the CLRWDT instruction was executed.

- In either case, the TO\_bit (4\_bit of STATUS register) will be set to indicate that the device Reset or wake-up event was due to a WDT time-out.

- □ If the WDT wakes the CPU from Sleep mode, the SLEEP status bit (bit\_3 of status register) will also be set to indicate that the device was previously in a Power-Saving mode

#### STATUS REGISTER

| R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0 | R/W-0                                                                                                           | R-1        | R-1                         | R/W-x | R/W-x | R/W-x |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------|------------|-----------------------------|-------|-------|-------|--|

| IRP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RP1   | RP0                                                                                                             | TO         | PD                          | Z     | DC    | С     |  |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       | •                                                                                                               |            |                             |       |       | bit 0 |  |

| Image: Section 1         Image: Section 2           Image: Section 2         Image: Section 2           Image: Section 2 | bit 4 | TO: Time-out bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT time-out occurred |            |                             |       |       |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 3 | PD: Powe                                                                                                        | r-down bit |                             |       |       |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |                                                                                                                 |            | r by the CLR<br>he SLEEP in |       | ion   |       |  |

#### WDT PERIOD

- □ The WDT has a nominal time-out period of 18 ms, (with no prescaler).

- The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs).

- □ If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION\_REG register. Thus, time-out periods up to 2.3 seconds can be realized.

- The CLRWDT and SLEEP instructions clear the WDT and the postscaler (if assigned to the WDT) and prevent it from timing out and generating a device RESET condition.

- □ The TO bit in the STATUS register will be cleared upon a WDT time-out.

For exp; 1/128 WDT\_rate, time\_out period= 128\*18ms=2,3 second.

#### **OPTION REGISTER (ADDRESS 81h)**

|   | R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|---|-------|--------|-------|-------|-------|-------|-------|-------|

| Γ | RBPU  | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

|   | bit 7 |        |       |       | •     |       |       | bit 0 |

| bit 3 PSA: Prescale | r Assignment bit |

|---------------------|------------------|

|---------------------|------------------|

bit 2-0

1 = Prescaler is assigned to the WDT

o = Prescaler is assigned to the Timer0 module

PS2:PS0: Prescaler Rate Select bits

Bit Value TMR0 Rate WDT Rate

| 000 | 1:2   | 1:1     |

|-----|-------|---------|

| 001 | 1:4   | 1:2     |

| 010 | 1:8   | 1:4     |

| 011 | 1:16  | 1:8     |

| 100 | 1:32  | 1:16    |

| 101 | 1:64  | 1:32    |

| 110 | 1:128 | 1:64    |

| 111 | 1:256 | 1 : 128 |

|     |       |         |

#### Example

Write a program to increment the value of PORTB from 00. Every 1152 ms, PORTB get started counting again from 00.