# MECE336 Microprocessors I PIC16F84A

Dr. Kurtuluş Erinç Akdoğan

kurtuluserinc@cankaya.edu.tr

Course Webpage: http://MECE336.cankaya.edu.tr

ÇANKAYA ÜNİVERSİTESİ MEKATRONİK MÜHENDİSLİĞİ BÖLÜMÜ

# CONTENT

□ In this lecture we will learn about:

- The PIC mid-range family, in overview.

- The overall architecture of the 16F84A.

- The 16F84A memory system, along with a review of memory technologies.

- Other hardware features of the 16F84A, including the reset system.

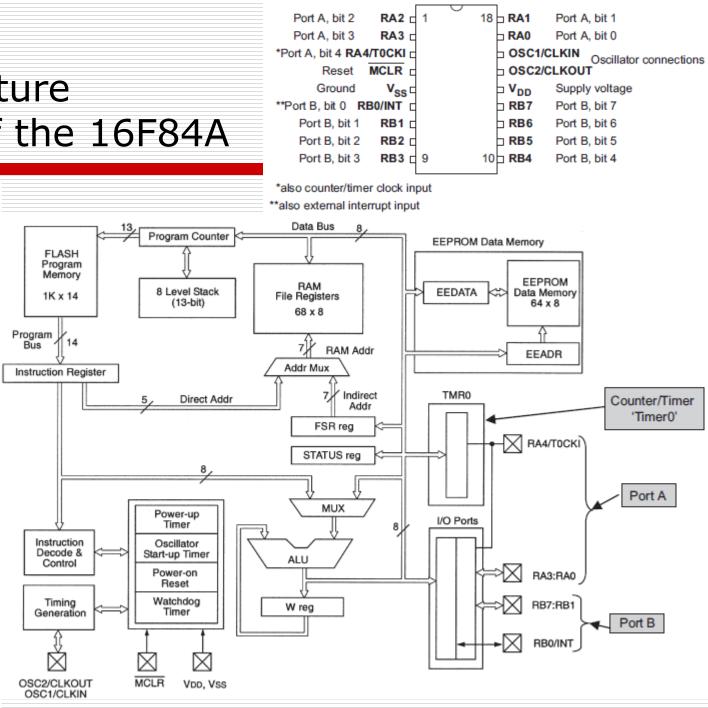

### An architecture overview of the 16F84A

-18 pins offers several functions to dedicate -program address bus is 13-bit allowing 2<sup>13</sup> (8192) locations in memory to address -the instruction word size is 14-bit

-Program memory size, at 1K, is however only one eighth of this. -EEPROM for program Memory allows programming rapidly and repeatedly changed -There are two digital input/output ports, Port A, with five pins, and Port B, with eight. -Bit 0 of Port B is shared with the external interrupt input.

# The Status Register

- The result of any CPU operation is held in the Working register

- What happens when the 8-bit range has been exceeded in an addition instruction, for example by adding binary numbers 1000 0000 and 1111 1101?

- The Working register has no way of indicating this and would simply hold an incorrect result.

- □ There are flags held in the Status register suc as bits C, DC and Z

|       | R/W-0           | R/W-0                    | R/W-0                         | R-1           | R-1          | R/W-x         | R/W-x          | R/W-x         |

|-------|-----------------|--------------------------|-------------------------------|---------------|--------------|---------------|----------------|---------------|

|       | IRP             | RP1                      | RP0                           | TO            | PD           | Z             | DC             | С             |

| bi    | t 7             |                          |                               |               |              |               |                | bit 0         |

| oit 2 | Z: Zei          |                          |                               |               |              |               |                |               |

|       | 0 = T           | he result of             | an arithmeti<br>an arithmeti  | c or logic op | eration is r | not zero      | _              |               |

| it 1  |                 | Digit Carry/bo<br>ersed) | orrow bit (AD                 | DWF, ADDLW    | , SUBLW, S   | UBWF instruc  | tions) (for bo | orrow, the po |

|       |                 |                          | rom the 4th I<br>from the 4th |               |              |               |                |               |

| bit 0 | C: Ca<br>revers | -                        | bit (ADDWF, 2                 | ADDLW, SUB    | LW, SUBWF    | instructions) | (for borrow    | , the polarit |

|       | 1               |                          | rom the Mos                   | t Significant | Bit of the r | eult occurre  | Ч              |               |

### A Review Of Memory Technologies

#### □ Static RAM (SRAM) is

- Volatile

- mainly used for data memory (RAM) in a microcontroller.

- EPROM (Erasable Programmable Read-Only Memory) technology is

- non-volatile.

- erased by exposing it to intense ultraviolet light.

- EEPROM (Electrically Erasable Programmable Read-Only Memory) is

- non-volatile.

- erased electrically.

- written to and erased on a byte-by-byte basis

- Flash is

- non-volatile.

- erased electrically.

- written to and erased on a block-by-block basis

- Used in latest products suc as USB Drives, solid-state drives

!!!Microchip organized so that a section of memory cells are erased in a single action or «flash».

## EEPROM vs FLASH MEMORY

| EEPROM                                                 | Flash Memory              |

|--------------------------------------------------------|---------------------------|

| Electrically Erasable Programmable Read<br>Only Memory | Solid State Disk          |

| NOR cells                                              | NAND cells                |

| Less Write More Read                                   | Both Read Write           |

| More Expensive                                         | Less Expensive            |

| Faster Read                                            | Slower Read               |

| More Time For Programming                              | Less Time For Programming |

| Less Voltage                                           | More Voltage              |

| Less Erasing Time                                      | More Erasing Time         |

| Erase Byte                                             | Erase Block or Whole chip |

| Smaller Faster Data                                    | Large Data                |

# PIC Overview: Memory

- Program Memory Data Memory

- Flash

RAM File registers

- Program Counter

- Stack

EEPROM

# The 16F84A Memory

- There are no less than four areas of memory in the 16F84A.

- Each memory has its own distinct function and means of access.

| Memory function                 | Technology | Size                | Volatile/<br>non volatile | Special<br>characteristics <sup>*</sup>            |

|---------------------------------|------------|---------------------|---------------------------|----------------------------------------------------|

| Program                         | Flash      | $1K \times 14$ bits | Non volatile              | 10 000 erase/write cycles, typically               |

| Data memory<br>(file registers) | SRAM       | 68 bytes            | Volatile                  | Retains data down<br>to supply voltage of<br>1.5 V |

| Data memory<br>(EEPROM)         | EEPROM     | 64 bytes            | Non volatile              | 10 000 000 erase/<br>write cycles,<br>typically    |

| Stack                           | SRAM       | $8 \times 13$ bits  | Volatile                  |                                                    |

|                                 |            |                     |                           |                                                    |

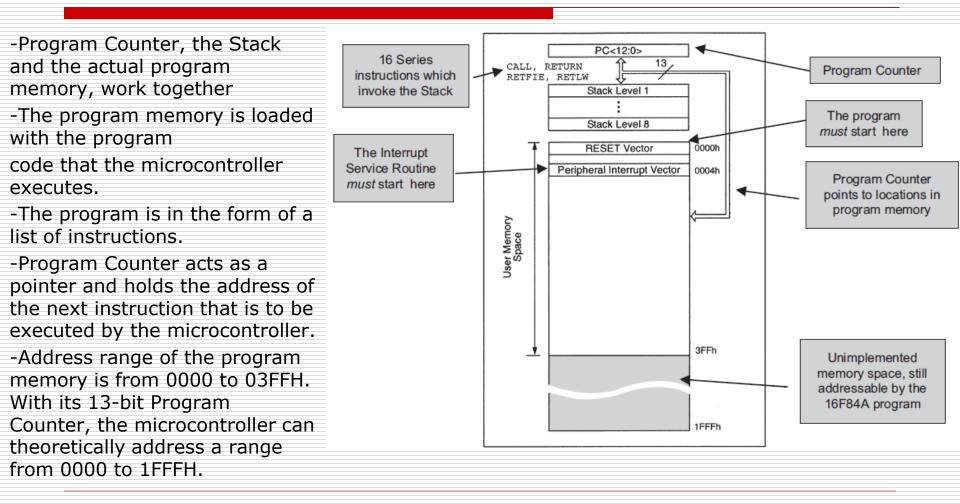

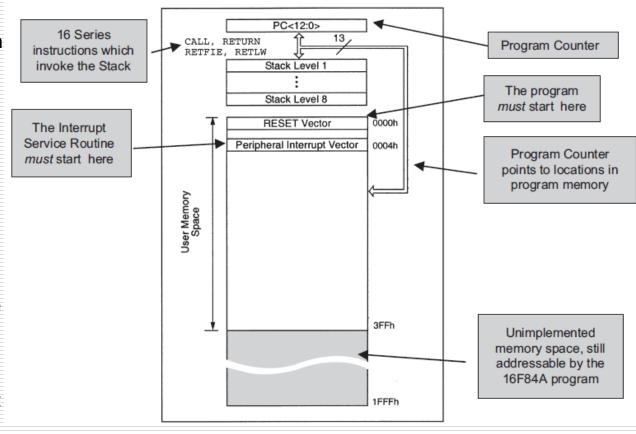

# Program Memory And The Stack

# Program Memory And The Stack

-Stack is a temporary memory that stores values of the program counter in case of special instructions (CALL, RETURN) -Stack is structured as LIFO memory – last in, first out -'reset vector' is first location in the program memory. -When the program starts running for the first time, for example on power-up, the Program Counter is set to 0000. -The programmer must therefore place his/her first instruction at this location. -The 'peripheral interrupt vector' acts in a similar way for interrupt

acts in a similar way for in service routines

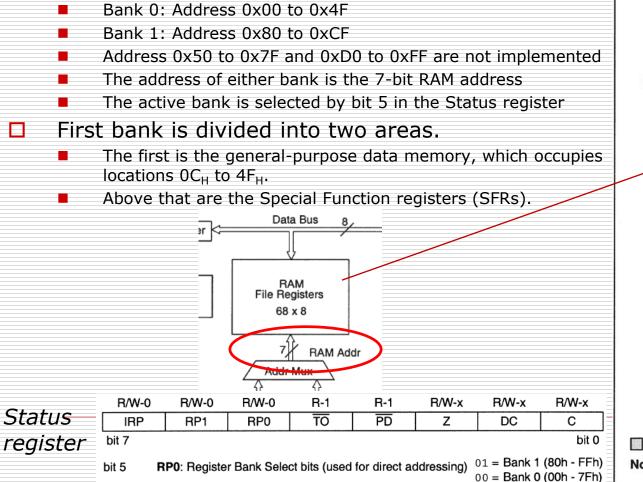

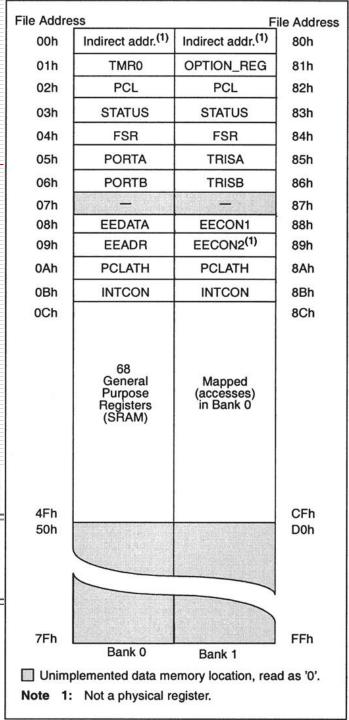

### Data and Special Function Register Memory (RAM)

The memory area is composed of two banks to

use less number of bits for addressing.

п

| File Address      |                                                 |                                   |            |  |  |  |  |  |  |

|-------------------|-------------------------------------------------|-----------------------------------|------------|--|--|--|--|--|--|

| 00h               | Indirect addr.(1)                               | Indirect addr. <sup>(1)</sup>     | 80h        |  |  |  |  |  |  |

| 01h               | TMR0                                            | OPTION_REG                        | 81h        |  |  |  |  |  |  |

| 02h               | PCL                                             | PCL                               | 82h        |  |  |  |  |  |  |

| 03h               | STATUS                                          | STATUS                            | 83h        |  |  |  |  |  |  |

| 04h               | FSR                                             | FSR                               | 84h        |  |  |  |  |  |  |

| 05h               | PORTA                                           | TRISA                             | 85h        |  |  |  |  |  |  |

| 06h               | PORTB                                           | TRISB                             | 86h        |  |  |  |  |  |  |

| 07h               | -                                               |                                   | 87h        |  |  |  |  |  |  |

| 08h               | EEDATA                                          | EECON1                            | 88h        |  |  |  |  |  |  |

| 09h               | EEADR                                           | EECON2 <sup>(1)</sup>             | 89h        |  |  |  |  |  |  |

| 0Ah               | PCLATH                                          | PCLATH                            | 8Ah        |  |  |  |  |  |  |

| 0Bh               | INTCON                                          | INTCON                            | 8Bh        |  |  |  |  |  |  |

| 0Ch               |                                                 |                                   | 8Ch        |  |  |  |  |  |  |

|                   | 68<br>General<br>Purpose<br>Registers<br>(SRAM) | Mapped<br>(accesses)<br>in Bank 0 |            |  |  |  |  |  |  |

| 4Fh<br>50h        |                                                 |                                   | CFh<br>D0h |  |  |  |  |  |  |

|                   |                                                 |                                   |            |  |  |  |  |  |  |

|                   |                                                 |                                   |            |  |  |  |  |  |  |

| 7Fh               | Bank 0                                          | Bank 1                            | FFh        |  |  |  |  |  |  |

| Dunimp<br>Note 1: | blemented data me<br>Not a physical re          | emory location, rea               | id as '0'. |  |  |  |  |  |  |

|                   |                                                 |                                   |            |  |  |  |  |  |  |

#### **Special Function Registers**

- cofigure interaction between CPU and peripherals.

- Each bit is wired across to one or other of the microcontroller peripherals.

- Each is then used either to set up the operating mode of the peripheral or to transfer data between the peripheral and the microcontroller core. As

| File Addre | ss                                              | F                                 | ile Address |

|------------|-------------------------------------------------|-----------------------------------|-------------|

| 00h        | Indirect addr.(1)                               | Indirect addr.(1)                 | 80h         |

| 01h        | TMR0                                            | OPTION_REG                        | 81h         |

| 02h        | PCL                                             | PCL                               | 82h         |

| 03h        | STATUS                                          | STATUS                            | 83h         |

| 04h        | FSR                                             | FSR                               | 84h         |

| 05h        | PORTA                                           | TRISA                             | 85h         |

| 06h        | PORTB                                           | TRISB                             | 86h         |

| 07h        | —                                               | —                                 | 87h         |

| 08h        | EEDATA                                          | EECON1                            | 88h         |

| 09h        | EEADR                                           | EECON2 <sup>(1)</sup>             | 89h         |

| 0Ah        | PCLATH                                          | PCLATH                            | 8Ah         |

| 0Bh        | INTCON                                          | INTCON                            | 8Bh         |

| 0Ch        |                                                 |                                   | 8Ch         |

|            | 68<br>General<br>Purpose<br>Registers<br>(SRAM) | Mapped<br>(accesses)<br>in Bank 0 |             |

| 4Fh<br>50h |                                                 |                                   | CFh<br>D0h  |

|            |                                                 |                                   |             |

| 7Fh        | Bank 0                                          | Bank 1                            | FFh         |

|            |                                                 |                                   | ad ac '0'   |

| Note 1:    | blemented data me<br>Not a physical re          |                                   | iu as U.    |

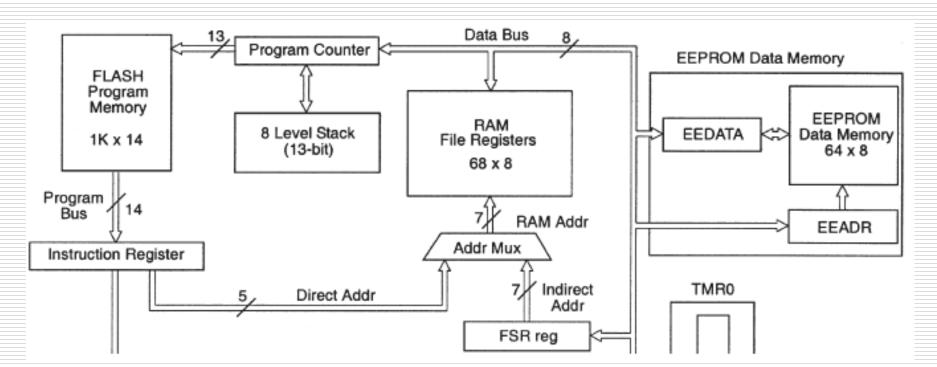

#### RAM addressing

Program

Bus

14

Instruction Register

There are two possible sources of the RAM address, selected through the address multiplexer ('Addr Mux'). Direct: part of the instruction Indirect: taken from the File Select Register (FSR) File address is 8 bit, MSB determines the bank. 7-bit from address bus from + 1 bit from status registers Or 5 bit from instruction. 57 Program Memory RAM 8 Level Stack 1K x 14 File Registers (13-bit) 68 x 8

Direct Addr

5

7∦

Addr Mux

RAM Addr

Indirect

Addr

FSR reg

# The Configuration Word

- This allows the user to define certain configurable features of the microcontroller, at the time of program download.

- These are fixed until the next time the microcontroller is programmed.

- it is not accessible within the program or in any way while the program is running.

| R/P-u    | R/P-u                                                                                                      | R/P-u | R/P-u | R/P-u | R/P-u | R/P-u   | R/P-u       | R/P-u                                                                                                                          | R/P-u                                                                                                       | R/P-u | R/P-u | R/P-u | R/P-u |

|----------|------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| CP       | СР                                                                                                         | CP    | СР    | CP    | CP    | CP      | CP          | CP                                                                                                                             | CP                                                                                                          | PWRTE | WDTE  | F0SC1 | F0SC0 |

| bit13    |                                                                                                            |       |       |       |       |         |             |                                                                                                                                |                                                                                                             |       |       |       | bit0  |

| bit 13-4 | <b>CP:</b> Code Protection bit<br>1 = Code protection disabled<br>0 = All program memory is code protected |       |       |       |       |         | bit 3       | 1                                                                                                                              | <b>PWRTE</b> : Power-up Timer Enable bit<br>1 = Power-up Timer is disabled<br>0 = Power-up Timer is enabled |       |       |       |       |

| bit 2    | WDTE: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled                                     |       |       |       |       | bit 1-0 | 1<br>1<br>( | FOSC1:FOSC0: Oscillator Selection bits<br>11 = RC oscillator<br>10 = HS oscillator<br>01 = XT oscillator<br>00 = LP oscillator |                                                                                                             |       |       |       |       |

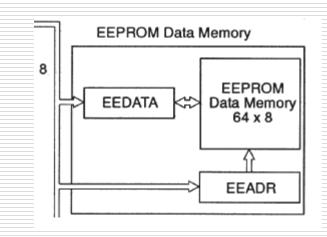

### EEPROM

- The EEPROM is non-volatile and is particularly useful for holding data variables that can be changed but are likely to be needed for the medium to long term.

- Examples include TV tuner settings, phone numbers stored in a cell phone or calibration settings on a measuring instrument

- In the 16F84A (and indeed any PIC microcontroller), the EEPROM is not placed in the main data memory map. Instead (as the top right of Figure 2.2 neatly shows) it is addressed through the EEADR register and data is transferred through the EEDATA register. These are both SFRs,

- reading from EEPROM is a simple process but writing to it is not